# VSC8244 Data Sheet

#### Quad 10/100/1000BASE-T PHY with RGMII and RTBI MAC Interfaces

## 1 General Description

Ideally suited for high port density Gigabit Ethernet switches and routers, or multi-port Network Interface Cards (NICs), Vitesse's VSC8244 integrates four low-power, triple speed (10BASE-T, 100BASE-TX, and 1000BASE-T) Ethernet transceivers in thermally-enhanced, 260-pin plastic Ball Grid Array (BGA).

The VSC8244 physical layer "PHY" IC leverages Vitesse's proprietary 4th generation DSP Technology. Vitesse's highly optimized DSP architecture yields industry leading performance at less than 640mW per port, supporting 1000BASE-T with respect to all worst case impairments (NEXT, FEXT, Echo, and system noise sources).

Each of the four independent triple-speed transceivers features pin-efficient RGMII and RTBI compliant MAC interfaces. On-chip RGMII/RTBI series termination resistors simplify board design challenges by improving signal integrity

and completely eliminating dozens of external series termination resistors on the receive side of the MAC interface. In addition, the VSC8244 integrates, for the first time in the industry, all copper media side line termination resistors.

To enable maximum network management feedback to the host system and the user, the VeriPHY® Link Management and Cable Diagnostics Suite can be used with the device. VeriPHY provides extensive network and cable plant operating and status information, such as the cable length, termination status, and open/short fault location. VeriPHY integrates with NIC or switch software to greatly simplify Gigabit Ethernet network deployment and management by providing the functionality equivalent to a hand-held cable tester.

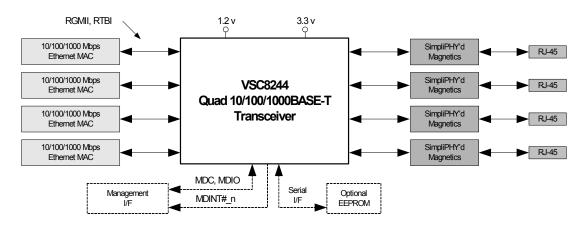

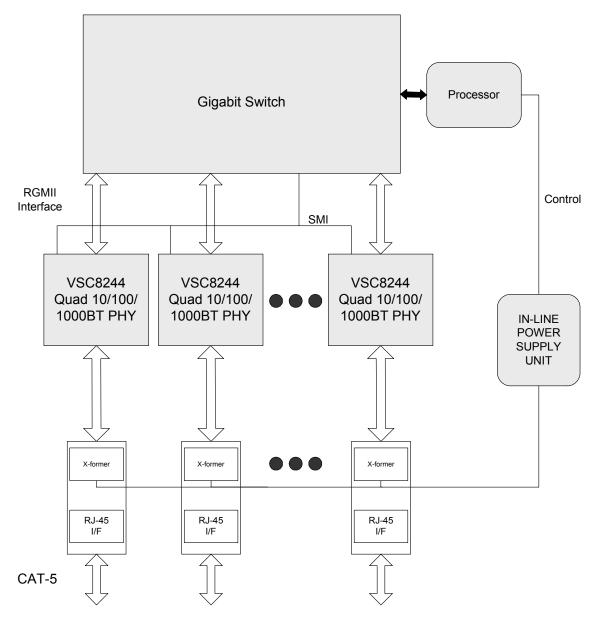

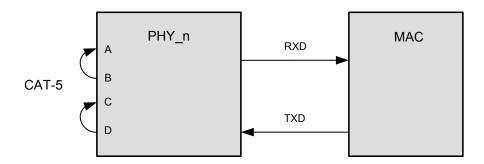

## 2 System Diagrams

Figure 1. VSC8244 System Diagram

| 3 | Features                                                                                                                             |   | Benefits                                                                                                                            |

|---|--------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------|

| • | Quad, low power, 10/100/1000BASE-T in a 19mm HS-BGA package                                                                          | • | Catalyzes market for low-cost & high density LAN, WAN, SAN, & MAN switches                                                          |

| • | Lowest power consumption in the industry at less than 640mW/port (1000BASE-T mode)                                                   | • | Eliminates heatsinks and fans for Gigabit to the desktop LAN switches                                                               |

| • | Supports PICMG 2.16 and 3.0 Ethernet backplanes at less than 500 mW/port                                                             | • | Lowest power mode reduces supply costs                                                                                              |

|   | Patented, low EMI line driver with integrated line side termination resistors                                                        |   | Removes 12 passive components per PHY*, reducing PCB area & cost by 50%                                                             |

|   |                                                                                                                                      |   | Saves up to 50% on magnetic module cost with SimpliPHY'd magnetics                                                                  |

|   |                                                                                                                                      | • | Enables magnetic-less PICMG backplane designs                                                                                       |

| • | Supports RGMII v1.3 (2.5V & 3.3V) & v2.0 (1.5V HSTL)                                                                                 | • | Compatible with a wide variety of parallel I/F switch ICs                                                                           |

| • | User-programmable RGMII timing compensation                                                                                          | • | Simplifies PCB layout; eliminates PCB trombones                                                                                     |

| • | Compliant with IEEE 802.3 (10BASE-T, 100BASE-TX, 1000BASE-T) specifications                                                          | • | Ensures seamless deployment throughout copper networks with industry's highest tolerance to noise and substandard cable plants      |

| • | >10kB jumbo frame support with programmable synchronization FIFOs                                                                    | • | Provides for maximum jumbo frame sizes in custom SAN and LAN systems                                                                |

| • | Five Direct drive LEDs per port with on-chip filtering or serial LED interface option                                                | • | Eliminates external components and EMI issues                                                                                       |

| • | Three user configuration options: 1) optional serial EEPROM, 2) hardware configuration pins, or 3) Serial Management Interface (SMI) | • | Offers design engineer a solution to fit any unmanaged or managed system requirement                                                |

| • | Full suite of BIST, near-end, and far-end loopback modes                                                                             | • | Simplifies comprehensive in-system test to ensure highest product quality                                                           |

| • | VeriPHY <sup>®</sup> cable diagnostics                                                                                               | • | Pin-points potential cable plant problems by providing equivalent diagnostic capabilities of a sophisticated hand-held cable tester |

| • | Automatic detection and correction of cable pair swaps,                                                                              | • | Compatible with 1st generation 1000BASE-T PHYs.                                                                                     |

|   | pair skew and pair polarity, along with HP Auto MDI/<br>MDI-X crossover function                                                     | • | Supports Auto MDI/MDI-X even when Autonegotiation is disabled                                                                       |

| • | Manufactured in advanced 0.13μm, 3.3V/1.2V digital CMOS process                                                                      | • | Most cost effective technology eliminates more expensive analog process variants                                                    |

|   |                                                                                                                                      |   | * or, 576 components for a 48-port switch                                                                                           |

# 4 Applications

- High Port Density 10/100/1000BASE-T Switches

- · Workgroup LAN Switches & Routers

- Backplane Applications such as PICMG 2.16, 3.0

- Gigabit Ethernet-based SAN, NAS, and MAN Systems

- High Performance Workstations & Multi-Port Server NICs

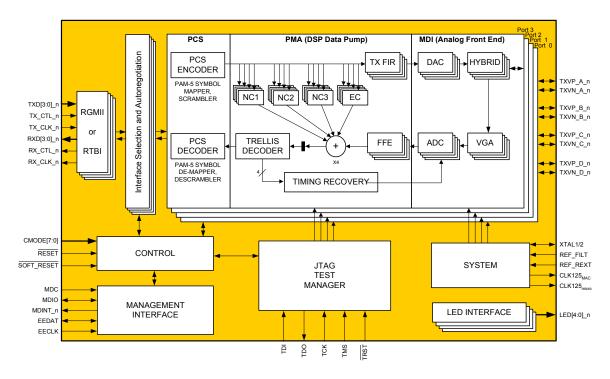

# 5 Device Block Diagram

Figure 2. VSC8244 Block Diagram<sup>1</sup>

$<sup>^{1}</sup>$ n = port number (0, 1, 2, 3)

# Contents

| 1   | General Description1 |                                                      |    |  |

|-----|----------------------|------------------------------------------------------|----|--|

| 2   | Syst                 | em Diagrams                                          | 1  |  |

| 3   | Features Benefits    |                                                      |    |  |

| 4   | Appl                 | ications                                             | 2  |  |

| 5   | Devi                 | ce Block Diagram                                     | 3  |  |

| 6   | Rele                 | vant Specifications & Documentation                  | 12 |  |

| 7   | VSC                  | 8244 Differences vs. VSC8224/VSC8234 Devices         | 13 |  |

|     | 7.1                  | VSC8244 Functional Differences                       | 13 |  |

|     | 7.2                  | VSC8244 Register Differences                         | 13 |  |

|     | 7.3                  | VSC8244 Pinout Differences                           | 14 |  |

| 8   | Data                 | Sheet Conventions                                    | 14 |  |

| 9   | Pack                 | age Pin Assignments & Signal Descriptions            | 15 |  |

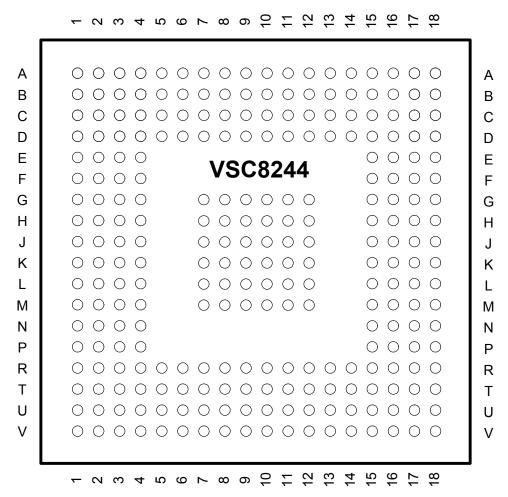

|     | 9.1                  | 260 HS-PBGA Package Ball Diagram                     | 15 |  |

|     | 9.2                  | BGA Ball to Signal Name Cross Reference (LEFT side)  | 16 |  |

|     | 9.3                  | BGA Ball to Signal Name Cross Reference (RIGHT side) | 17 |  |

|     | 9.4                  | Signal Type Descriptions                             | 18 |  |

|     | 9.5                  | MAC Transmit Interface (MAC TX) Pins                 | 19 |  |

|     | 9.6                  | MAC Receive Interface (MAC RX) Pins                  |    |  |

|     | 9.7                  | Twisted Pair Interface Pins                          |    |  |

|     | 9.8                  | Serial Management Interface Pins (IEEE SMI)          |    |  |

|     | 9.9                  | Serial EEPROM Interface Pins                         |    |  |

|     | 9.10                 | Configuration and Control Pins                       |    |  |

|     | 9.11                 | System Clock Interface Pins                          |    |  |

|     | 9.12                 | LED Interface Pins                                   |    |  |

|     | 9.13                 | JTAG Test Access Port Pins                           |    |  |

|     | 9.14                 | Analog Bias Pins                                     |    |  |

|     |                      | HSTL Voltage Reference Pins                          |    |  |

|     | 9.16                 | No Connect Pins                                      |    |  |

|     | 9.17<br>9.18         | Power Supply Pins                                    |    |  |

| 4.0 |                      |                                                      |    |  |

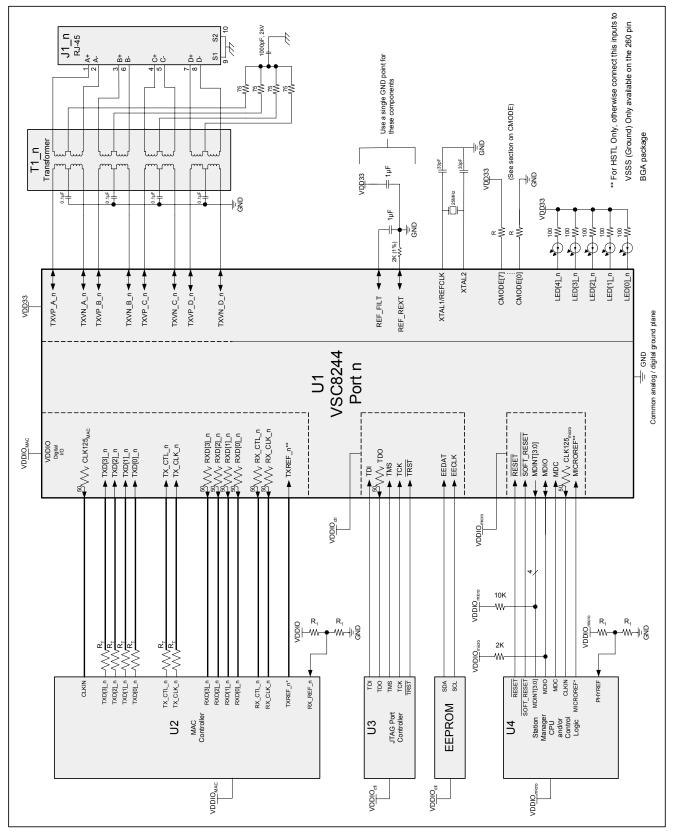

| 10  | •                    | em Schematics                                        |    |  |

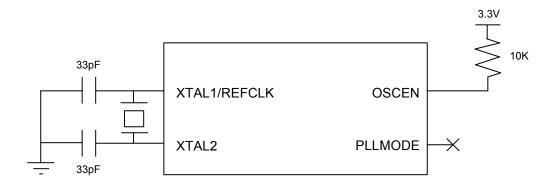

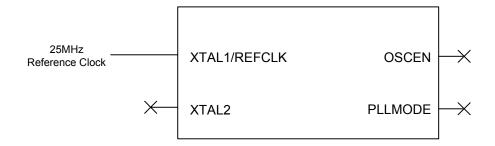

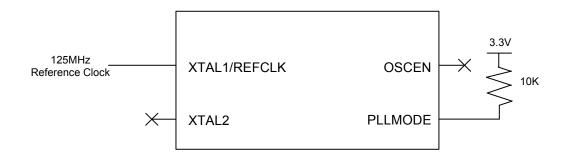

|     | 10.1                 | Input Clock Options                                  |    |  |

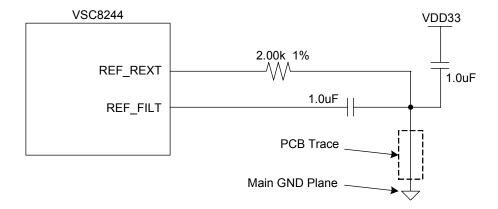

|     |                      | Analog Bias Pins Configuration                       |    |  |

| 11  | MAC                  | Interfaces                                           |    |  |

|     | 11.1                 | RGMII MAC I/F                                        |    |  |

|     | 11.2                 | RTBI MAC I/F                                         | 32 |  |

| 12 | 2 Twisted Pair Interface                                                       | 22    |

|----|--------------------------------------------------------------------------------|-------|

| 14 | 12.1 Twisted Pair Autonegotiation (IEEE802.3 Clause 28)                        |       |

|    | 12.1 Twisted Pair Auto MDI/MDI-X Function                                      |       |

|    | 12.3 Auto MDI/MDI-X in Forced 10/100 Link Speeds                               |       |

|    | 12.4 Twisted Pair Link Speed Downshift                                         |       |

|    | ·                                                                              |       |

| 13 | 3 Transformerless Ethernet Operation for PICMG 2.16 and 3.0 IP-based Backplane | es 35 |

| 14 | Serial Management Interface (SMI)                                              | 35    |

|    | 14.1 SMI Interrupt                                                             | 36    |

| 15 | Parallel LED Interface                                                         | 38    |

| 16 | S Serial LED Output                                                            | 41    |

| 17 | 7 Test Mode Interface (JTAG)                                                   | 42    |

| •  | 17.1 Supported Instructions and Instruction Codes                              |       |

|    | 17.2 Boundary-Scan Register Cell Order                                         |       |

|    | , .                                                                            |       |

| 18 | 3 VeriPHY Cable Diagnostics                                                    |       |

|    | 18.1 Coupling Between Cable Pairs                                              |       |

|    | 18.2 Cable Pair Termination                                                    |       |

|    | 18.3 Cable Length                                                              |       |

|    | 18.4 Using VeriPHY in normal operating mode                                    | 45    |

| 19 | ActiPHY Power Management                                                       | 46    |

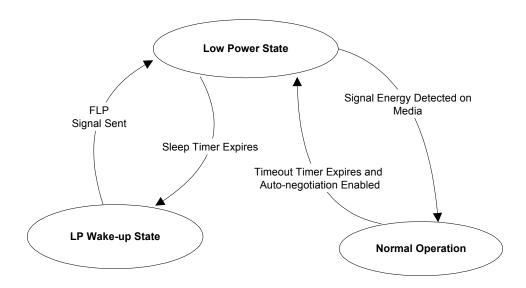

|    | 19.1 Operation in ActiPHY Mode                                                 | 46    |

|    | 19.2 Low power state                                                           | 47    |

|    | 19.3 LP Wake up state                                                          | 47    |

|    | 19.4 Normal operating state                                                    | 47    |

| 20 | Ethernet In-line Powered Device Support                                        | 48    |

|    | 20.1 Cisco In-Line Powered Device Detection                                    | 48    |

|    | 20.2 In-Line Power Ethernet Switch Diagram                                     | 48    |

|    | 20.3 In-Line Powered Device Detection (Cisco Method)                           | 49    |

|    | 20.4 IEEE 802.3af (DTE Power via MDI)                                          | 49    |

| 21 | Advanced Test Modes                                                            | 49    |

|    | 21.1 Ethernet Packet Generator (EPG)                                           | 49    |

|    | 21.2 CRC Counter                                                               | 49    |

|    | 21.3 Far-end Loopback                                                          | 50    |

|    | 21.4 Near-end Loopback                                                         | 50    |

|    | 21.5 Connector Loopback                                                        | 51    |

| 22 | 2 Initialization & Configuration                                               | 52    |

|    | 22.1 Resets                                                                    | 52    |

|    | 22.2 Power-Up Sequence                                                         | 52    |

|    | 22.3 CMODE Pin Configuration                                                   | 52    |

|    | 22.4 EEPROM Interface                                                          | 55    |

| 23 | MII R | Register Set                                                                | 61 |

|----|-------|-----------------------------------------------------------------------------|----|

|    | 23.1  | MII Extended Page Registers                                                 | 62 |

|    | 23.3  | MII Register Quick Reference                                                | 63 |

|    | 23.4  | MII Register Quick Reference - Extended Page Mode                           | 65 |

| 24 | MII R | Register Descriptions                                                       | 66 |

|    | 24.1  | Register 0 (00h) – Mode Control Register                                    | 66 |

|    | 24.2  | Register 1 (01h) – Mode Status Register                                     |    |

|    | 24.3  | Register 2 (02h) – PHY Identifier Register #1                               | 67 |

|    | 24.4  | Register 3 (03h) – PHY Identifier Register #2                               |    |

|    | 24.5  | Register 4 (04h) – Auto-Negotiation Advertisement Register                  | 68 |

|    | 24.6  | Register 5 (05h) – Auto-Negotiation Link Partner Ability Register           |    |

|    | 24.7  | Register 6 (06h) – Auto-Negotiation Expansion Register                      |    |

|    | 24.8  | Register 7 (07h) – Auto-Negotiation Next-Page Transmit Register             | 69 |

|    | 24.9  | Register 8 (08h) – Auto-Negotiation Link Partner Next-Page Receive Register | 69 |

|    | 24.10 | Register 9 (09h) – 1000BASE-T Control Register                              | 70 |

|    |       | Register 10 (0Ah) – 1000BASE-T Status Register                              |    |

|    | 24.12 | Register 11 (0Bh) – Reserved Register                                       | 72 |

|    |       | Register 12 (0Ch) – Reserved Register                                       |    |

|    | 24.14 | Register 13 (0Dh) – Reserved Register                                       | 72 |

|    | 24.15 | Register 14 (0Eh) – Reserved Register                                       | 73 |

|    | 24.16 | Register 15 (0Fh) – 1000BASE-T Status Extension Register #1                 | 73 |

|    |       | Register 16 (10h) – 100BASE-TX Status Extension Register                    |    |

|    | 24.18 | Register 17 (11h) – 1000BASE-T Status Extension Register #2                 | 74 |

|    |       | Register 18 (12h) – Bypass Control Register                                 |    |

|    | 24.20 | Register 19 (13h) – Reserved                                                | 77 |

|    | 24.21 | Register 20 (14h) – Reserved                                                | 77 |

|    | 24.22 | Register 21 (15h) – Reserved                                                | 77 |

|    | 24.23 | Register 22 (16h) – Extended Control & Status Register                      | 78 |

|    | 24.24 | Register 23 (17h) – Extended PHY Control Register #1                        | 79 |

|    | 24.25 | Register 24 (18h) – Extended PHY Control Register #2                        | 81 |

|    | 24.26 | Register 25 (19h) – Interrupt Mask Register                                 | 83 |

|    | 24.27 | Register 26 (1Ah) – Interrupt Status Register                               | 84 |

|    | 24.28 | Register 27 (1Bh) – LED Control Register                                    | 86 |

|    | 24.29 | Register 28 (1Ch) – Auxiliary Control & Status Register                     | 87 |

|    | 24.30 | Register 29 (1Dh) – Reserved                                                | 89 |

|    | 24.31 | Register 30 (1Eh) - Reserved                                                | 89 |

|    | 24.32 | Register 31 (1Fh) – Extended Page Access                                    | 89 |

|    | 24.33 | Register 16E (10h) - Reserved                                               | 90 |

|    | 24.34 | Register 17E (11h) - CLK125micro Clock Enable                               | 90 |

|    |       | Register 18E (12h) - Reserved                                               |    |

|    |       | 8 Register 19E (13h) - Reserved                                             |    |

|    |       | Register 20E (14h) - Extended PHY Control Register #3                       |    |

|    |       | Register 21E (15h) - EEPROM Interface Status and Control Register           |    |

|    | 24.39 | Register 22E (16h) - EEPROM Data Read/Write Register                        | 93  |

|----|-------|-----------------------------------------------------------------------------|-----|

|    | 24.40 | Register 23E (17h) - Extended PHY Control Register #4                       | 93  |

|    | 24.41 | Register 24E (18h) – Reserved                                               | 94  |

|    | 24.42 | Register 25E (19h) – Reserved                                               | 94  |

|    | 24.43 | Register 26E (1Ah) – Reserved                                               | 94  |

|    | 24.44 | Register 27E (1Bh) – Reserved                                               | 94  |

|    | 24.45 | Register 28E (1Ch) – Reserved                                               | 94  |

|    | 24.46 | Register 29E (1Dh) - 1000BASE-T Ethernet Packet Generator (EPG) Register #1 | 95  |

| 25 | Elect | rical Specifications                                                        | 96  |

|    | 25.1  | Absolute Maximum Ratings                                                    | 96  |

|    | 25.2  | Recommended Operating Conditions                                            | 97  |

|    | 25.3  | Thermal Application Data                                                    | 98  |

|    | 25.4  | Package Thermal Specifications - 260 HS-PBGA                                | 98  |

|    | 25.5  | Current and Power Consumption Estimates                                     | 99  |

|    | 25.6  | DC Specifications                                                           | 100 |

|    | 25.7  | Clocking Specifications                                                     | 102 |

|    | 25.8  | System Timing Specifications                                                | 103 |

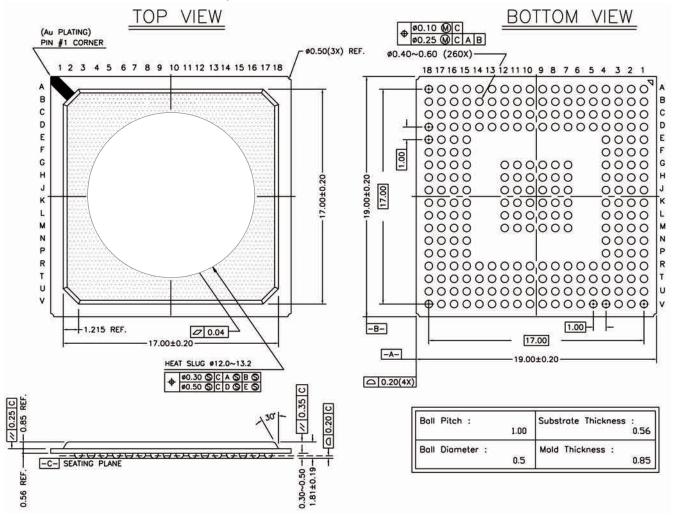

| 26 | Pack  | aging Specifications                                                        | 115 |

|    | 26.1  | 19mm HS-PBGA Mechanical Specification                                       | 115 |

|    | 26.2  | Package Moisture Sensitivity                                                | 115 |

| 27 | Orde  | ring Information                                                            | 116 |

|    | 27.1  | Devices                                                                     | 116 |

|    | 27.2  | Related Devices                                                             | 116 |

| 28 | Desi  | gn Guidelines                                                               | 117 |

|    | 28.1  | Required SMI Register Write Sequence                                        | 117 |

|    | 28.2  | Interoperability with Intel 82547E1 L322SQ96                                | 117 |

| 29 | Prod  | uct Support                                                                 | 119 |

|    | 29.1  | Available Documents and Application Notes                                   | 119 |

| 30 | Docu  | ment History & Notices                                                      | 120 |

# **Figures**

| Figure 1.  | VSC8244 System Diagram                                          | 1   |

|------------|-----------------------------------------------------------------|-----|

| Figure 2.  | VSC8244 Block Diagram                                           | 3   |

| Figure 3.  | 260 HS-PBGA Package Ball Diagram                                | 15  |

| Figure 4.  | 260-Pin HS-PBGA (19mm) Signal Map (TOP LEFT side of package)    | 16  |

| Figure 5.  | 260-Pin HS-PBGA (19mm) Signal Map (TOP RIGHT side of package)   | 17  |

| Figure 6.  | General System Schematic (shown with RGMII and 3.3V I/O)        | 28  |

| Figure 7.  | Crystal Clock Option                                            | 29  |

| Figure 8.  | 25 MHz Reference Clock Option                                   | 29  |

| Figure 9.  | 125 MHz Reference Clock Option                                  | 30  |

| Figure 10. | Analog Bias Pins Ground Connection Diagram                      | 30  |

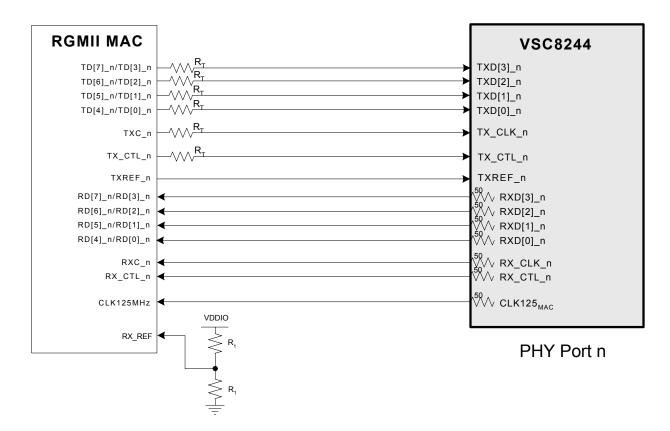

| Figure 11. | RGMII MAC Interface                                             | 31  |

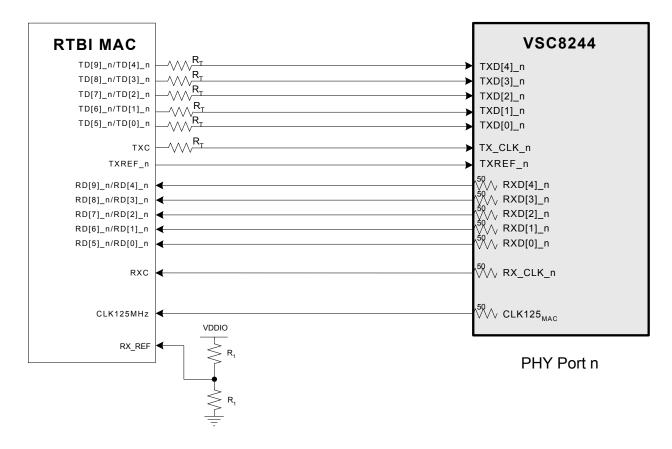

| Figure 12. | RTBI MAC Interface                                              | 32  |

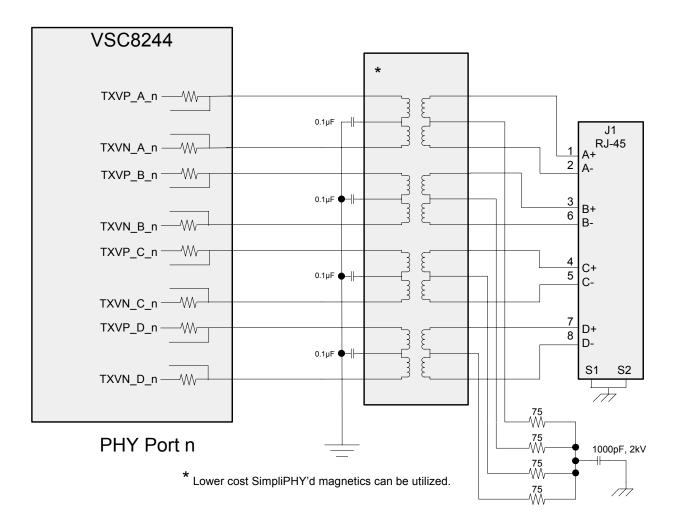

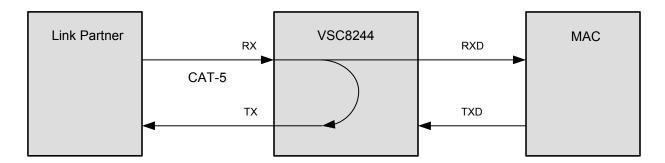

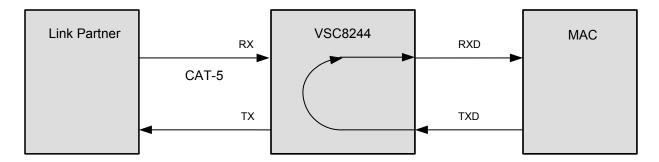

| Figure 13. | Twisted Pair Interface                                          | 33  |

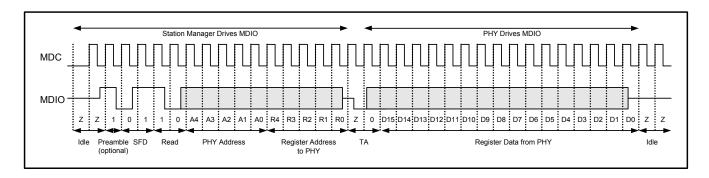

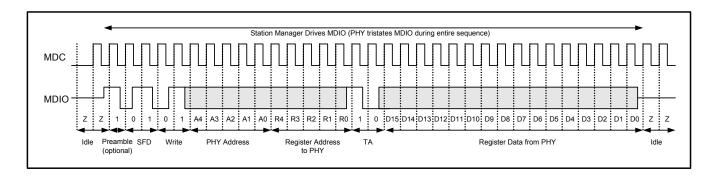

| Figure 14. | MDIO Read Frame                                                 | 36  |

| Figure 15. | MDIO Write Frame                                                | 36  |

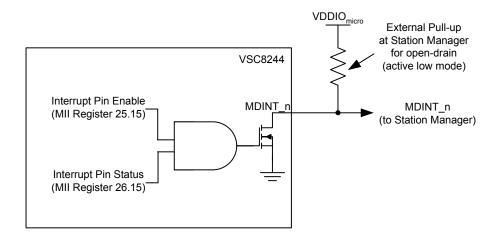

| Figure 16. | Logical Representation of Open-Drain (Active-Low) MDINT_n Pin   | 37  |

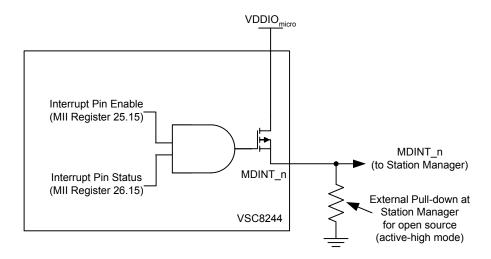

| Figure 17. | Logical Representation of Open-Source (Active-High) MDINT_n Pin | 37  |

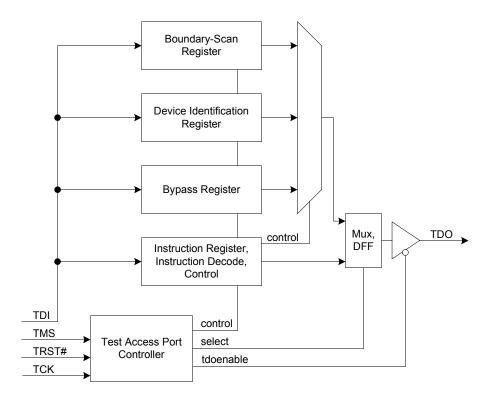

| Figure 18. | Test Access Port and Boundary Scan Architecture                 | 42  |

| Figure 19. | ActiPHY State Diagram                                           | 46  |

| Figure 20. | In-line Powered Ethernet Switch Diagram                         | 48  |

| Figure 21. | Far-end Loopback Block Diagram                                  | 50  |

| Figure 22. | Near-end Loopback Block Diagram                                 | 50  |

| Figure 23. | Connector Loopback                                              | 51  |

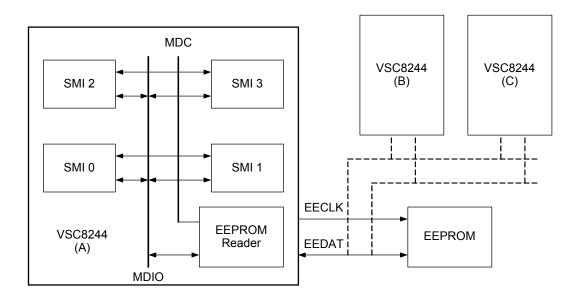

| Figure 24. | VSC8244 Devices Connected to use the same Startup EEPROM        | 57  |

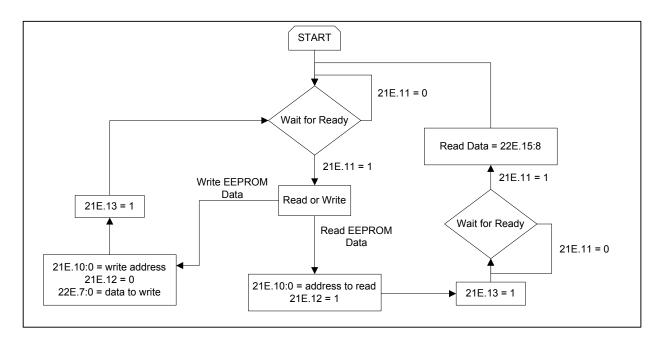

| Figure 25. | EEPROM Read and Write Register Flow                             | 60  |

| Figure 26. | Extended Page Register                                          | 62  |

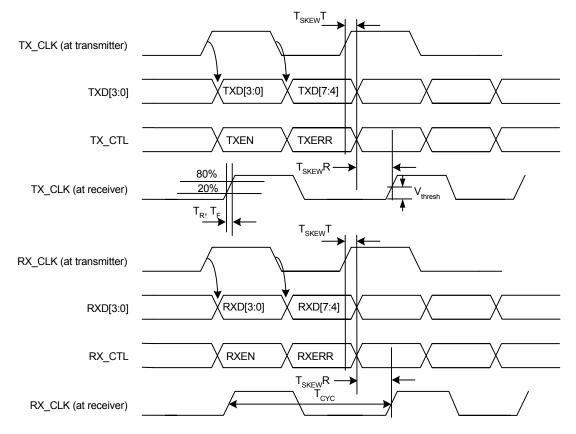

| Figure 27. | RGMII Uncompensated AC Timing and Multiplexing                  | 104 |

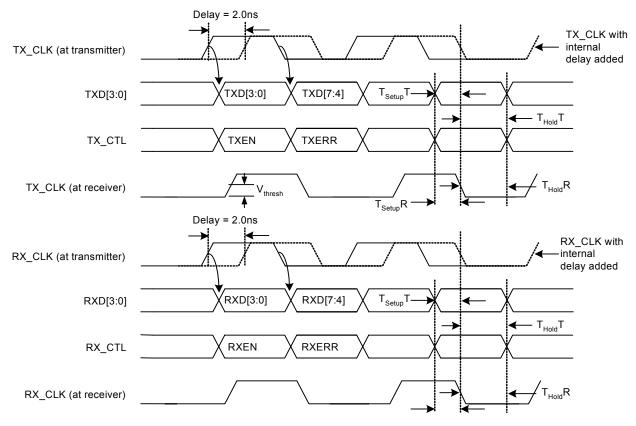

| Figure 28. | RGMII Compensated AC Timing and Multiplexing                    | 105 |

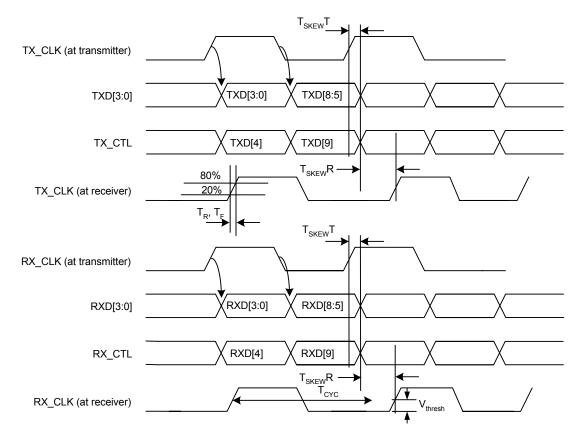

| Figure 29. | RTBI Uncompensated AC Timing and Multiplexing                   | 107 |

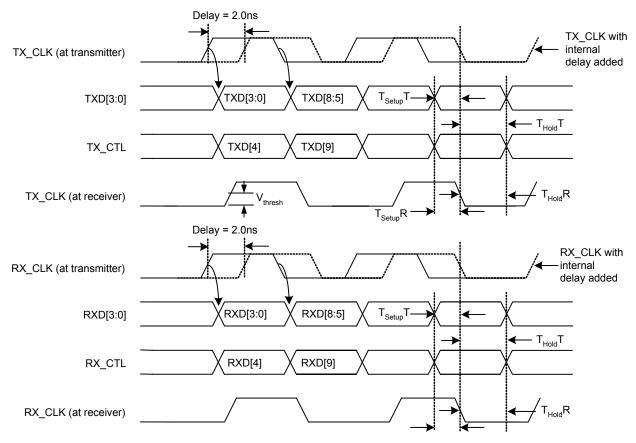

| Figure 30. | RTBI Compensated AC Timing and Multiplexing                     | 108 |

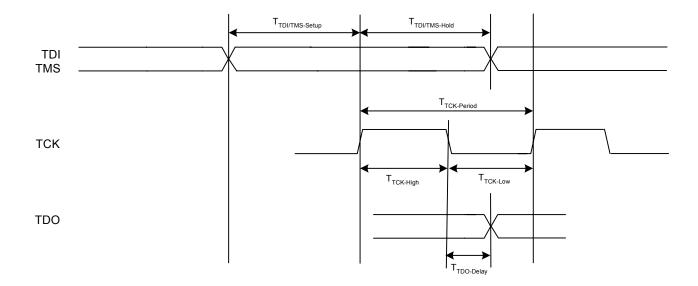

| Figure 31. | JTAG Interface AC Timing                                        | 109 |

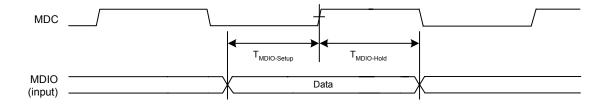

| Figure 32. | SMI AC Timing                                                   | 110 |

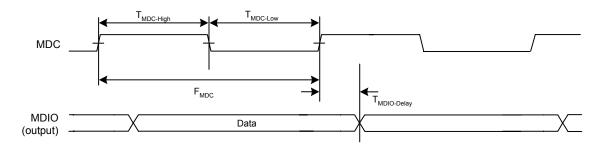

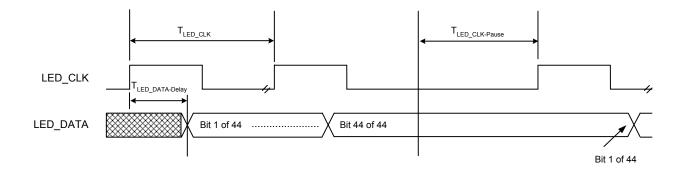

| Figure 33. | LED_CLK and LED_DATA Output AC Timing                           | 111 |

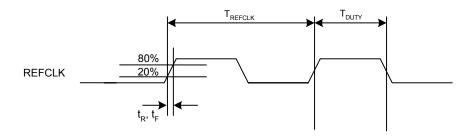

| Figure 34. | REFCLK AC Timing                                                | 112 |

## VSC8244 Data Sheet

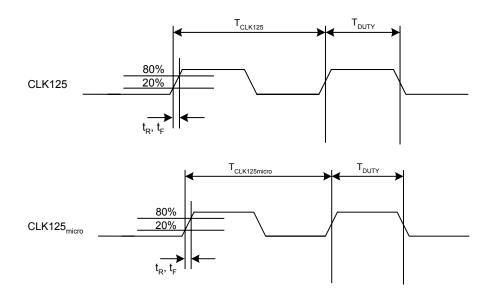

| Figure 35. | CLK125 AC Timing                      | 113 |

|------------|---------------------------------------|-----|

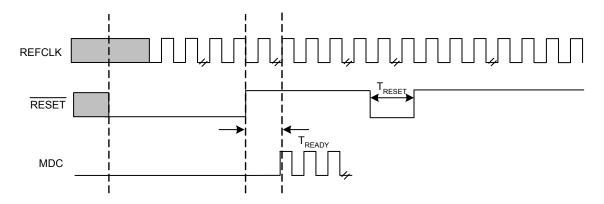

| Figure 36. | RESET AC Timing                       | 114 |

| Figure 37. | 19mm HS-PBGA Mechanical Specification | 115 |

# **Tables**

| Table 1.  | VSC8244 Relevant Specifications                               | 12 |

|-----------|---------------------------------------------------------------|----|

| Table 2.  | VSC8224/VSC8234/VSC8244 MAC / Media Interface Support Options | 13 |

| Table 3.  | Data Sheet Conventions                                        | 14 |

| Table 4.  | Signal Type Descriptions                                      | 18 |

| Table 5.  | MAC TX Signal Descriptions                                    | 19 |

| Table 6.  | MAC RX Signal Descriptions                                    | 20 |

| Table 7.  | Twisted Pair Interface Pins                                   | 21 |

| Table 8.  | Serial Management Interface Pins                              | 22 |

| Table 9.  | Serial EEPROM Interface Pins                                  | 23 |

| Table 10. | Configuration and Control Pins                                | 23 |

| Table 11. | System Clock Interface Pins                                   | 24 |

| Table 12. | LED Interface Pins                                            | 24 |

| Table 13. | JTAG TAP Signal Descriptions                                  | 25 |

| Table 14. | Analog Bias Pins                                              | 25 |

| Table 15. | HSTL Voltage Reference Pins                                   | 25 |

| Table 16. | No Connect Pins                                               | 26 |

| Table 17. | Power Supply Pins                                             | 26 |

| Table 18. | Power Supply and Associated Functional Pins                   | 27 |

| Table 19. | Accepted MDI Pair Connection Combinations                     | 34 |

| Table 20. | SMI Frame Format                                              | 35 |

| Table 21. | LED Function Assignments                                      | 38 |

| Table 22. | LED Functions                                                 | 38 |

| Table 23. | LED Output Options                                            | 40 |

| Table 24. | Serial LED Output Data                                        | 41 |

| Table 25. | JTAG Device Identification Register Description               | 43 |

| Table 26. | JTAG Interface Instruction Codes                              | 43 |

| Table 27. | CMODE Hardware Configuration Bits                             | 53 |

| Table 28. | CMODE Pin Combinations                                        | 53 |

| Table 29. | CMODE Configuration Bits                                      | 54 |

| Table 30. | EEPROM Configuration Contents                                 | 55 |

| Table 31. | EEPROM Configuration Contents for Multiple VSC8244 Devices    | 57 |

| Table 32. | MII Register Bit Modes                                        | 61 |

| Table 33. | MII Register Quick Reference                                  | 63 |

| Table 34. | MII Register Quick Reference - Extended Page Mode             | 65 |

| Table 35. | Transmitter/Receiver Test Mode                                                        | 70  |

|-----------|---------------------------------------------------------------------------------------|-----|

| Table 36. | Test Mode 4                                                                           | 71  |

| Table 37. | Transmitter Test Clock Enable                                                         | 76  |

| Table 38. | MAC/Media Interface Mode Select                                                       | 80  |

| Table 39. | Thermal Air Flow Specifications - 260 ball HSBGA 19mm package                         | 98  |

| Table 40. | Thermal Specifications - 260 ball HSBGA 19mm package                                  | 98  |

| Table 41. | Current and Power Consumption Estimates - HSTL @ 1.5V, RGMII mode, no LEDs, no CLK125 | 99  |

| Table 42. | Current and Power Consumption Estimates - 2.5V, RGMII mode, no LEDs, no CLK125        | 99  |

| Table 43. | Current and Power Consumption Estimates - 3.3V, RGMII mode, no LEDs, no CLK125        | 99  |

| Table 44. | Digital Pins Specifications (VDDIO = 3.3V)                                            | 100 |

| Table 45. | Digital Pins Specifications (VDDIO = 2.5V)                                            | 100 |

| Table 46. | Digital Pins Specifications (VDDIO = 1.5V)                                            | 101 |

| Table 47. | LED Output Pins Specifications                                                        | 102 |

| Table 48. | Reference Clock Option Specifications                                                 | 102 |

| Table 49. | Crystal Option Specifications                                                         | 103 |

| Table 50. | RGMII Mode AC Timing Specifications                                                   | 103 |

| Table 51. | RTBI Mode AC Timing Specifications                                                    | 106 |

| Table 52. | JTAG Interface AC Timing Specifications                                               | 109 |

| Table 53. | SMI AC Timing Specifications                                                          | 110 |

| Table 54. | MDINT AC Timing Specifications                                                        | 111 |

| Table 55. | LED_CLK and LED_DATA Output AC Timing Specification                                   | 111 |

| Table 56. | REFCLK AC Timing Specifications                                                       | 112 |

| Table 57. | CLK125 AC Timing Specifications                                                       | 113 |

| Table 58. | RESET AC Timing Specification                                                         | 114 |

| Table 59. | Startup Write Sequence Changes                                                        | 117 |

| Table 60. | Startup Write Sequence Changes for Intel 82547E1 Interoperability                     | 118 |

| Table 61. | Document Revision History                                                             | 120 |

# 6 Relevant Specifications & Documentation

The VSC8244 conforms to the following specifications. Please refer to these documents for additional information.

Table 1. VSC8244 Relevant Specifications

| Specification - Revision                   | Description                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE 802.3-2002                            | Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications. IEEE 802.3-2002 consolidates and supersedes the following specifications: 802.3ab (1000BASE-T), 802.3u (Fast Ethernet), with references to ANSI X3T12 TP-PMD standard (ANSI X3.263 TP-PMD). |

| IEEE 1149.1-1990                           | Test Access Port and Boundary Scan Architecture <sup>1</sup> . Includes IEEE Standard 1149.1a-1993 and IEEE Standard 1149.1b-1994.                                                                                                                                                                            |

| JEDEC EIA/JESD8-5                          | 2.5V±0.2V (Normal Range), and 1.8V to 2.7V (Wide Range) Power Supply Voltage and Interface Standard for Nonterminated Digital Integrated Circuits.                                                                                                                                                            |

| JEDEC JESD22-A114-B                        | Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM). Revision of JESD22-A114-A.                                                                                                                                                                                                          |

| JEDEC JESD22-A115-A                        | Electrostatic Discharge (ESD) Sensitivity Testing Machine Model (MM). Revision of EIA/JESD22-A115.                                                                                                                                                                                                            |

| JEDEC EIA/JESD78                           | IC Latch-Up Test Standard.                                                                                                                                                                                                                                                                                    |

| MIL-STD-883E                               | Miltary Test Method Standard for Microcircuits.                                                                                                                                                                                                                                                               |

| RGMII Specification - v1.3, v2.0           | Reduced Pin-Count Interface for Gigabit Ethernet Physical Layer Devices (per Hewlett Packard). Includes both RGMII and RTBI standards.                                                                                                                                                                        |

| PICMG 2.16                                 | IP Backplane specification for CompactPCI v2.16.                                                                                                                                                                                                                                                              |

| Advanced TCA™ Base<br>PICMG 3.0            | IP Backplane specification for CompactPCI v3.0.                                                                                                                                                                                                                                                               |

| Cisco InLine Power Detection<br>Algorithmn | Cisco Sytems InLine Power Detection: http://www.cisco.com/en/US/products/hw/phones/ps379/ products_tech_note09186a00801189b5.shtml                                                                                                                                                                            |

<sup>&</sup>lt;sup>1</sup> Often referred to as the "JTAG" test standard.

## 7 VSC8244 Differences vs. VSC8224/VSC8234 Devices

The VSC8244 is one of three, quad port PHY devices featuring Vitesse's proprietary fourth-generation DSP technology. It provides parallel RGMII/RTBI interfaces and 10/100/1000BASE-T Category-5, Unshielded Twisted Pair (UTP) copper media interfaces. The VSC8234 features serial SGMII/SerDes MAC interfaces with Category-5 UTP media interfaces. The VSC8224 is the dual media capable device featuring RGMII/RTBI parallel MAC interfaces with support for both 10/100/1000BASE-T and 1000BASE-X media interfaces.

The following table summarizes the MAC and media interfaces supported by the VSC8244, the VSC8234, and the VSC8244 quad-port PHY:

| Device # | MAC Interface       | Media Interface     | Package Options  | Full Part Number |

|----------|---------------------|---------------------|------------------|------------------|

| VSC8224  | RGMII / RTBI        | CAT-5               | 260 pin HS DRCA  | VSC8224HG        |

| V3C0224  | RGMII / RTBI        | SerDes (1000Base-X) | 260-pin HS-PBGA  | V3C022411G       |

| VSC8234  | SGMII (4 or 6 pin)  | CAT-5               | 260-pin HS-PBGA  | VSC8234HG        |

| V3C0234  | SerDes (1000Base-X) | CAT-5               | 200-piii HS-PBGA | V3C6234FIG       |

| VSC8244  | RGMII / RTBI        | CAT-5               | 260-pin HS-PBGA  | VSC8244HG        |

Table 2. VSC8224/VSC8234/VSC8244 MAC / Media Interface Support Options

#### 7.1 VSC8244 Functional Differences

The VSC8244 is a functional subset of the VSC8224 in that it provides all the same features except for the following:

- No media side SerDes interfaces for supporting 1000BASE-X (fiber).

- Differences in the CMODE configurations settings as certain functions in the VSC8224 relating to the serial interface are not present in the VSC8244. This includes several MAC interfaces, SIGDET direction setting, and SerDes termination impedance setting

#### 7.2 VSC8244 Register Differences

The VSC8244 is the exact register map equivalent to the VSC8224's register map with the following exceptions:

- · Register 3: Device number indication changes to VSC8244.

- Register 23:

- Bit 15 is Reserved and must be set to 0.

- Bits 14:12 less modes are present. Only modes involving RGMII-CAT5 and RTBI-CAT5 exist in the VSC8244.

- Register 24: TXFIFO settings only affect RGMII as opposed to SerDes and SGMII as in the VSC8224.

- Register 25 & 26: Bit 4 for the Auto-Media Sense (AMS) indication condition is not available.

- Register 16E: Only bits 2:0 (Remote Fault bit settings) are relevant on the VSC8244.

- Register 20E: Bits 7:5 related to AMS and SerDes termination impedance for the VSC8224 are not present in the VSC8224.

#### 7.3 VSC8244 Pinout Differences

The 260-pin HS-PBGA packages between the VSC8224HG and the VSC8244HG are the exact same (pin-for-pin compatible), except for the following pins:

The following pins are NC on the VSC8244HG 260-pin HS-PBGA:

- Pins T1, M1, H1, D1, U1, N1, J1, E1 -- TDP/N\_[3:0] signals

- Pins R1, L1, G1, C1, P1, K1, F1, B1 -- RDP/N\_[3:0] signals

- Pins R2, L2, G2, C2, T2, M2, H2, D2 -- RCP/N\_[3:0] signals

- Pins E2, J2, N2, U2 -- SIGDET\_[3:0] signals

## 8 Data Sheet Conventions

Conventions used throughout this data sheet are specified in the following table.

**Table 3. Data Sheet Conventions**

| Convention                            | Syntax                                                | Examples                | Description                                                                                          |

|---------------------------------------|-------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|

| Register<br>number                    | RegisterNumber.Bit<br>or<br>RegisterNumber.BitRange   | 23.10<br>23.12:10       | Register 23 (address 17h), bit 10.<br>Register 23 (address 17h), bits 12, 11, and 10.                |

| Extended<br>Page Regis-<br>ter number | RegisterNumberE.Bit<br>or<br>RegisterNumberE.BitRange | 23E.10<br>23E.12:10     | Extended Register 23 (address 17h), bit 10. Extended Register 23 (address 17h), bits 12, 11, and 10. |

| Signal name (active high)             | SIGNALNAME <sup>1</sup>                               | PLLMODE                 | Signal name for PLLMODE.                                                                             |

| Signal name (active low)              | SIGNALNAME <sup>1</sup>                               | RESET                   | Active low reset signal.                                                                             |

| Signal bus name                       | BUSNAME[MSB:LSB] <sup>1</sup>                         | CMODE[4:0] <sup>2</sup> | CMODE configuration bits 4, 3, 2, 1, and 0.                                                          |

| PHY port number                       | _n                                                    | _3                      | Denotes a specific PHY port #3. n= {3    2    1   0}.                                                |

| PHY-specific port signal              | SIGNALNAME_n <sup>1</sup>                             | RX_CTL_3                | RX_CTL signal for PHY port 3 <sup>3</sup> .                                                          |

| Signal bus for a specific PHY port    | SIGNALNAME[MSB:LSB]_n <sup>1</sup>                    | RXD[3:0]_3              | Receive data bus, bits 3through 0, for PHY port #3 <sup>3</sup> .                                    |

<sup>&</sup>lt;sup>1</sup> All signal names are in all CAPITAL LETTERS.

<sup>&</sup>lt;sup>2</sup> CMODE is common to entire device.

<sup>&</sup>lt;sup>3</sup> RXD signals are unique to each PHY.

## 9 Package Pin Assignments & Signal Descriptions

#### 9.1 260 HS-PBGA Package Ball Diagram

For complete specifications, refer to Section 26: "Packaging Specifications".

260 HS-PBGA 1.0mm Ball Pitch (19mm body size) (Top View)

Figure 3. 260 HS-PBGA Package Ball Diagram

(View from top of package with underlying BGA ball positions superimposed)

## 9.2 BGA Ball to Signal Name Cross Reference (LEFT side)

|   | 1        | 2        | 3        | 4        | 5                    | 6                    | 7                    | 8        | 9                    |

|---|----------|----------|----------|----------|----------------------|----------------------|----------------------|----------|----------------------|

| Α | LED[4]_3 | LED[0]_2 | TXVPD_3  | TXVPC_3  | TXVPB_3              | TXVPA_3              | TXVPD_2              | TXVPC_2  | TXVPB_2              |

| В | NC       | LED[1]_2 | TXVND_3  | TXVNC_3  | TXVNB_3              | TXVNA_3              | TXVND_2              | TXVNC_2  | TXVNB_2              |

| С | NC       | NC       | LED[2]_2 | LED[3]_2 | LED[4]_2             | NC                   | NC                   | VDD33    | REF_REXT             |

| D | NC       | NC       | LED[3]_3 | VDD33    | VDD33                | VDD33                | VSSS                 | VSSS     | VDD33                |

| E | NC       | NC       | LED[2]_3 | VDD12    |                      |                      |                      |          |                      |

| F | NC       | VSSS     | LED[1]_3 | VDD12    |                      |                      |                      |          |                      |

| G | NC       | NC       | LED[0]_3 | VSSS     |                      |                      | VSSS                 | VSSS     | VSSS                 |

| н | NC       | NC       | VDD12    | VDDDIG   |                      |                      | VSSS                 | VSSS     | VSSS                 |

| J | NC       | NC       | VDD12    | VDDDIG   |                      |                      | VSSS                 | VSSS     | VSSS                 |

| K | NC       | VSSS     | VSSS     | VSSS     |                      |                      | VSSS                 | VSSS     | VSSS                 |

| L | NC       | NC       | VSSS     | VDD33    |                      |                      | VSSS                 | VSSS     | VSSS                 |

| М | NC       | NC       | VDD12    | VSSS     |                      |                      | VSSIO                | VSSIO    | VSSIO                |

| N | NC       | NC       | VDD12    | VSSS     |                      |                      |                      |          |                      |

| Р | NC       | VSSS     | VSSS     | VDDDIG   |                      |                      |                      |          |                      |

| R | NC       | NC       | VDD12    | VDDDIG   | VDDIO <sub>MAC</sub> | VDDIO <sub>MAC</sub> | VDDIO <sub>MAC</sub> | TXREF_2  | VDDIO <sub>MAC</sub> |

| Т | NC       | NC       | TXREF_3  | RXD[2]_3 | TX_CLK_3             | TXD[2]_3             | RX_CLK_2             | RXD[2]_2 | TX_CLK_2             |

| U | NC       | NC       | RX_CTL_3 | RXD[1]_3 | TX_CTL_3             | TXD[1]_3             | RX_CTL_2             | RXD[1]_2 | TX_CTL_2             |

| v | NC       | RX_CLK_3 | RXD[3]_3 | RXD[0]_3 | TXD[3]_3             | TXD[0]_3             | RXD[3]_2             | RXD[0]_2 | TXD[3]_2             |

|   | 1        | 2        | 3        | 4        | 5                    | 6                    | 7                    | 8        | 9                    |

Figure 4. 260-Pin HS-PBGA (19mm) Signal Map (TOP LEFT side of package)

## 9.3 BGA Ball to Signal Name Cross Reference (RIGHT side)

| 10       | 11                   | 12                   | 13       | 14       | 15                     | 16       | 17                    | 18                                  |   |

|----------|----------------------|----------------------|----------|----------|------------------------|----------|-----------------------|-------------------------------------|---|

| TXVPA_2  | TXVPD_1              | TXVPC_1              | TXVPB_1  | TXVPA_1  | TXVPD_0                | TXVPC_0  | TXVPB_0               | TXVPA_0                             | A |

| TXVNA_2  | TXVND_1              | TXVNC_1              | TXVNB_1  | TXVNA_1  | TXVND_0                | TXVNC_0  | TXVNB_0               | TXVNA_0                             | В |

| REF_FILT | VSSS                 | VSSS                 | VSSS     | VSSS     | NC                     | CMODE[7] | CMODE[6]              | CMODE[5]                            | С |

| VDD33    | VDD33                | VDD33                | VDD33    | VDD12    | VDD12                  | CMODE[4] | XTAL1 or<br>REFCLK    | XTAL2                               | D |

|          |                      |                      |          |          | NC                     | CMODE[3] | CMODE[2]              | CMODE[1]                            | E |

|          |                      |                      |          |          | VDD33                  | CMODE[0] | LED[0]_1              | LED[1]_1                            | F |

| VSSS     | VSSS                 | VSSS                 |          |          | VDD33                  | LED[2]_1 | LED[3]_1              | LED[4]_1                            | G |

| VSSS     | VSSS                 | VSSS                 |          |          | VDDDIG                 | LED[0]_0 | LED[1]_0              | LED[2]_0                            | Н |

| VSSS     | VSSS                 | VSSS                 |          |          | VDDDIG                 | TDI      | LED[3]_0              | LED[4]_0                            | J |

| VSSS     | VSSS                 | VSSS                 |          |          | VDDIO <sub>ctl</sub>   | TDO      | TCK                   | TMS                                 | K |

| VSSS     | VSSS                 | VSSS                 |          |          | VDDIO <sub>micro</sub> | TRST     | EECLK or<br>PLLMODE   | EEDAT                               | L |

| VSSIO    | VSSIO                | VSSIO                |          |          | VSSIO                  | RESET    | SOFT_<br>RESET        | OSCEN or<br>CLK125 <sub>micro</sub> | M |

|          |                      |                      |          |          | VSSS                   | MDINT_1  | MDINT_2               | MDINT_3                             | N |

|          |                      |                      |          |          | VSSS                   | MDC      | MDIO                  | MDINT_0                             | P |

| TXREF_1  | VDDIO <sub>MAC</sub> | VDDIO <sub>MAC</sub> | TXREF_0  | VDDDIG   | VDDDIG                 | VDD33    | CLK125 <sub>MAC</sub> | MICROREF                            | R |

| TXD[2]_2 | RX_CLK_1             | RXD[0]_1             | TXD[3]_1 | TXD[0]_1 | RXD[3]_0               | RXD[0]_0 | TXD[3]_0              | TXD[0]_0                            | т |

| TXD[1]_2 | RX_CTL_1             | RXD[1]_1             | TX_CLK_1 | TXD[1]_1 | RX_CTL_0               | RXD[1]_0 | TX_CTL_0              | TXD[1]_0                            | U |

| TXD[0]_2 | RXD[3]_1             | RXD[2]_1             | TX_CTL_1 | TXD[2]_1 | RX_CLK_0               | RXD[2]_0 | TX_CLK_0              | TXD[2]_0                            | V |

| 10       | 11                   | 12                   | 13       | 14       | 15                     | 16       | 17                    | 18                                  |   |

Figure 5. 260-Pin HS-PBGA (19mm) Signal Map (TOP RIGHT side of package)

# 9.4 Signal Type Descriptions

**Table 4. Signal Type Descriptions**

| Symbol              | Signal Type                                                                                                                                                                              | Description                                                                                                                                                                                                        |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I                   | Digital Input                                                                                                                                                                            | Standard digital input signal. No internal pull-up or pull-down.                                                                                                                                                   |  |  |

| I <sub>PU</sub>     | Digital Input with Pull-up                                                                                                                                                               | Standard digital input. Includes on-chip 100k $\Omega$ pull-up to VDDIO.                                                                                                                                           |  |  |

| I <sub>PD</sub>     | Digital Input with Pull-down                                                                                                                                                             | Standard digital input. Includes on-chip 100kΩ pull-down to VSSIO.                                                                                                                                                 |  |  |

| O <sub>ZC</sub>     | Impedance Controlled Output                                                                                                                                                              | $50\Omega$ integrated (on-chip) source series terminated, digital output signal. Used primarily for timing-sensitive MAC I/F and 125MHz clock output pins, in addition to high speed manufacturing test mode pins. |  |  |

| I <sub>PD</sub> /O  | Digital Bidirectional                                                                                                                                                                    | Tristate-able, digital input and output signal. Includes on-chip 100k $\Omega$ pull-down to VSSIO.                                                                                                                 |  |  |

| OD                  | Digital Open Drain Output                                                                                                                                                                | Open drain digital output signal. Must be pulled to VDDIO through an external pullup resistor.                                                                                                                     |  |  |

| A <sub>DIFF</sub>   | Analog Differential                                                                                                                                                                      | Analog differential signal pair for twisted pair interface.                                                                                                                                                        |  |  |

| A <sub>BIAS</sub>   | Analog Bias                                                                                                                                                                              | Analog bias or reference signal. Must be tied to external resistor and/or capacitor bias network, as shown in Section 10: "System Schematics".                                                                     |  |  |

| I <sub>A</sub>      | Analog Input                                                                                                                                                                             | Analog input for sensing variable voltage levels.                                                                                                                                                                  |  |  |

| os                  | Open Source                                                                                                                                                                              | Open source digital output signal. Must be pulled to GND through an external pull-down resistor.                                                                                                                   |  |  |

| V <sub>REF</sub>    | Voltage Reference Input                                                                                                                                                                  | Voltage Reference input pins required for VDDIO HSTL mode.                                                                                                                                                         |  |  |

| I <sub>PUJTAG</sub> | JTAG input pin. Includes on-chip pullup to VDDIO <sub>CTL</sub> . These pins are 5V tol when VDDIO <sub>CTL</sub> = 3.3V. For VDDIO <sub>CTL</sub> = 2.5V, these pins are up to 4.7V tol |                                                                                                                                                                                                                    |  |  |

| O <sub>CRYST</sub>  | Crystal Output                                                                                                                                                                           | Crystal clock output pin. If not used, leave unconnected.                                                                                                                                                          |  |  |

| NC                  | No Connect No connect signal. Must be left floating.                                                                                                                                     |                                                                                                                                                                                                                    |  |  |

## 9.5 MAC Transmit Interface (MAC TX) Pins

The following pins are used for connecting to a parallel data bus MAC via the industry-standard RGMII and RTBI interfaces.

Table 5. MAC TX Signal Descriptions

| HSBGA<br>Ball #                                                                 | Signal Name MAC Interface Modes     |                                              |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  | Туре | Description |

|---------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|------|-------------|

| Buil II                                                                         | RGMII                               | RTBI                                         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |      |             |

| V5, T6, U6, V6<br>V9, T10, U10, V10<br>T13, V14, U14, T14<br>T17, V18, U18, T18 | TXD[3:0]_1                          | TXD[3:0]_2<br>TXD[3:0]_1                     | $I_{PD}$        | Multiplexed Transmit Data Nibbles (RGMII mode) Bits [3:0] are synchronously input on the rising edge of TX_CLK_n, and bits [7:4] on the falling edge of TX_CLK_n.  Multiplexed Transmit Data Nibbles (RTBI mode) Bits [3:0] are synchronously input on the rising edge of TX_CLK_n, and bits [8:5] on the falling edge of TX_CLK_n.                                                                                                                                                                                                                                                                                                                   |  |  |      |             |

| U5<br>U9<br>V13<br>U17                                                          | TX_CTL_3 TX_CTL_2 TX_CTL_1 TX_CTL_0 | TXD[4]_2<br>TXD[4]_1                         | I <sub>PD</sub> | Transmit Enable, Transmit Error Multiplexed Input (RGMII mode) In RGMII mode, this input is sampled by the PHY on opposite edges of TX_CLK_n to indicate two transmit conditions of the MAC: 1) on the rising edge of TX_CLK_n, this input serves as TXEN, indicating valid data is available on the TD input data bus. 2) on the falling edge of TX_CLK_n, this input signals a transmit error from the MAC, based on a logical derivative of TXEN and TXER, per RGMII specification Version 2.0.  Multiplexed Transmit Data (RTBI mode) Bit [4] is synchronously input on the rising edge of TX_CLK_n, and bit [9] on the falling edge of TX_CLK_n. |  |  |      |             |

| T5<br>T9<br>U13<br>V17                                                          | TX_CLK_2<br>TX_CLK_1                | TX_CLK_3<br>TX_CLK_2<br>TX_CLK_1<br>TX_CLK_0 | $I_{PD}$        | Transmit Clock Input (RGMII mode) The transmit clock shall be either a 125MHz or 25MHz (for 1000Mb or 100Mb modes, respectively), with a +/-50ppm tolerance. If left unconnected, these pins will require a pull-down resistor to ground.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |      |             |

# 9.6 MAC Receive Interface (MAC RX) Pins

All output pins for the MAC interface include impedance-calibrated, tristateable output drive capability.

Table 6. MAC RX Signal Descriptions

| HSBGA<br>Ball #                                                              | Signal<br>MAC Interf                         |                                              | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dall #                                                                       | RGMII                                        | RTBI                                         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V3, T4, U4, V4<br>V7, T8, U8, V8<br>V11, V12, U12, T12<br>T15, V16, U16, T16 | RXD[3:0]_1                                   | RXD[3:0]_2<br>RXD[3:0]_1                     | O <sub>ZC</sub> | Multiplexed Receive Data Nibble (RGMII mode only) Bits [3:0] are synchronously output on the rising edge of RX_CLK_n, and bits [7:4] on the falling edge of RX_CLK_n.  Multiplexed Receive Data Nibbles (RTBI mode) Bits [3:0] are synchronously output on the rising edge of RX_CLK_n, and bits [8:5] on the falling edge of RX_CLK_n.                                                                                                                                                                                                                                                                                                                                                                                  |

| V2<br>T7<br>T11<br>V15                                                       | RX_CLK_2<br>RX_CLK_1                         | RX_CLK_3<br>RX_CLK_2<br>RX_CLK_1<br>RX_CLK_0 |                 | Receive Clock Output (RGMII and RTBI modes) Receive data is sourced from the PHY synchronously on the rising edge of RX_CLK_n and is the recovered clock from the media.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| U3<br>U7<br>U11<br>U15                                                       | RX_CTL_3<br>RX_CTL_2<br>RX_CTL_1<br>RX_CTL_0 | RXD[4]_2                                     | O <sub>ZC</sub> | <ul> <li>Multiplexed Receive Data Valid / Receive Error Output (RGMII mode only). In RGMII mode, this output is sampled by the MAC on opposite edges of RX_CLK_n to indicate two receive conditions from the PHY:</li> <li>1) on the rising edge of RX_CLK_n, this output serves as RXDV, signaling valid data is available on the RD input data bus,</li> <li>2) on the falling edge of RX_CLK_n, this output signals a receive error from the PHY, based on a logical derivative of RXDV and RXER, per RGMII specification Version 2.0.</li> <li>Multiplexed Receive Data (RTBI mode)</li> <li>Bit [4] is synchronously output on the rising edge of RX_CLK_n, and bit [9] on the falling edge of RX_CLK_n.</li> </ul> |

## 9.7 Twisted Pair Interface Pins

Table 7. Twisted Pair Interface Pins

| HSBGA<br>Ball #         | Signal<br>Name                           | Туре              | Description                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A6<br>A10<br>A14<br>A18 | TXVPA_3<br>TXVPA_2<br>TXVPA_1<br>TXVPA_0 | A <sub>DIFF</sub> | TX/RX Channel "A" Positive Signal Positive differential signal connected to the positive primary side of the transformer. This pin signal forms the positive signal of the "A" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 1. See System Schematic.                               |

| B6<br>B10<br>B14<br>B18 | TXVNA_3<br>TXVNA_2<br>TXVNA_1<br>TXVNA_0 | A <sub>DIFF</sub> | TX/RX Channel "A" Negative Signal  Negative differential signal connected to the negative primary side of the transformer. This pin signal forms the negative signal of the "A" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 2. See System Schematic.                              |

| A5<br>A9<br>A13<br>A17  | TXVPB_3<br>TXVPB_2<br>TXVPB_1<br>TXVPB_0 | A <sub>DIFF</sub> | TX/RX Channel "B" Positive Signal Positive differential signal connected to the positive primary side of the transformer. This pin signal forms the positive signal of the "B" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 3. See System Schematic.                               |

| B5<br>B9<br>B13<br>B17  | TXVNB_3<br>TXVNB_2<br>TXVNB_1<br>TXVNB_0 | A <sub>DIFF</sub> | TX/RX Channel "B" Negative Signal  Negative differential signal connected to the negative primary side of the transformer. This pin signal forms the negative signal of the "B" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 6. See System Schematic.                              |

| A4<br>A8<br>A12<br>A16  | TXVPC_3<br>TXVPC_2<br>TXVPC_1<br>TXVPC_0 | A <sub>DIFF</sub> | TX/RX Channel "C" Positive Signal Positive differential signal connected to the positive primary side of the transformer. This pin signals forms the positive signal of the "C" data. In 1000Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 4 (pins not used in 10M/100M modes). See System Schematic.         |

| B4<br>B8<br>B12<br>B16  | TXVNC_3<br>TXVNC_2<br>TXVNC_1<br>TXVNC_0 | A <sub>DIFF</sub> | TX/RX Channel "C" Negative Signal  Negative differential signal connected to the negative primary side of the transformer. This pin signal forms the negative signal of the "C" data channel. In 1000Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 5 (pins not used in 10M/100M modes). See System Schematic. |

| A3<br>A7<br>A11<br>A15  | TXVPD_3<br>TXVPD_2<br>TXVPD_1<br>TXVPD_0 | A <sub>DIFF</sub> | TX/RX Channel "D" Positive Signal Positive differential signal connected to the positive primary side of the transformer. This pin signal forms the positive signal of the "D" data channel. In 1000Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 7 (pins not used in 10M/100M modes). See System Schematic.  |

| B3<br>B7<br>B11<br>B15  | TXVND_3<br>TXVND_2<br>TXVND_1<br>TXVND_0 | A <sub>DIFF</sub> | TX/RX Channel "D" Negative Signal Negative differential signal connected to the negative primary side of the transformer. This pin signal forms the positive signal of the "D" data channel. In 1000Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 8 (pins not used in 10M/ 100M modes). See System Schematic. |

# 9.8 Serial Management Interface Pins (IEEE SMI)

Table 8. Serial Management Interface Pins

| HSBGA<br>Ball            | Signal Name                              | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P16                      | MDC                                      | I         | Management Data Clock A 0 to 12.5MHz reference input is used to clock serial MDIO data into and out of the VSC8244. The expected nominal frequency is 2.5MHz, as specified by the IEEE standard. This clock is typically asynchronous with respect to the PHY's transmit or receive clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P17                      | MDIO                                     | OD        | Management Data I/O MDIO configuration and status data is exchanged on this pin bidirectionally between the PHY and the Station Manager, synchronously to the rising edge of MDC. This signal normally requires a 1.5k $\Omega$ to 2k $\Omega$ external pull-up resistor at the Station Manager. The value of the pull-up resistor depends on the MDC clock frequency and the maximum capacitive load on the MDIO pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| P18<br>N16<br>N17<br>N18 | MDINT_0<br>MDINT_1<br>MDINT_2<br>MDINT_3 | OS/<br>OD | Management Interrupt Outputs These output signals indicate a change in each of the four PHY's link operating conditions for which a station manager must interrogate to determine further information. Upon reset or powerup, the VSC8244 will automatically configure these pins as active-low (open drain) or active-high (open source) based on the polarity of an external resistor connection. For active-low configuration, tie each MDINT_n pin to VDD33 through an external $10k\Omega$ pull-up resistor. For active-high configuration, tie each MDINT_n pin to GND through an external $10k\Omega$ pull-down resistor. If only one MDINT_n signal is desired for all four PHYs, these pins can be tied together on the PCB in a wired-OR configuration with only a single pull-up or pull-down resistor. |

### 9.9 Serial EEPROM Interface Pins

Table 9. Serial EEPROM Interface Pins